1. Tujuan

[Kembali]

1. Untuk mengetahui dan menjelaskan J-K flip flop & toggle flip flop (T flip flop)

2. Untuk mensimulasikan rangkaian mengenai J-K flip flop & toggle flip flop (T flip flop)

2. Alat dan Bahan

[Kembali]

2.1 Alat

1. Power Supply

Resistor digunakan untuk menghambat arus listrik.

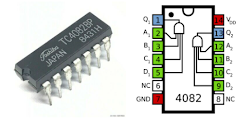

2. Gerbang AND

AND akan menghasilkan output berlogika 0 jika salah satu atau semua inputnya berlogika 0.

3. Gerbang NAND

Spesifikasi:

4. Gerbang NOT (Inverter)

Konfigurasi Pin:

Spesifikasi:3. Dasar Teori

[Kembali]

J-K Flip Flop

J-K Flip-flop merupakan pengembangan dari S-R Flip-flop. J-K Flip-flop memiliki 3 terminal input, yaitu J, K, dan Clk (Clock). J-K Flip flop ini dibagun dari rangkaian dasar S-R Flip Flop dengan menambahkan dua gerbang AND pada masukan S dan R serta dilengkapi dengan rangkaian diferensiator pembentuk denyut pulsa Clock (Clk).

Persamaan Output J-K Flip Flop berdasarkan peta Karnaugh :

1. J-K Flip Flop dengan Input PRESET dan CLEAR

Perlu untuk membersihkan flip flop ke status logika '0' (Qn=0) atau membuatnya ke status logika '1' (Qn=1). Contohnya seperti pada gambar 10.29.

2. Master-Slave Flip Flop

Master-slave flip-flop menghilangkan semua masalah waktu dengan menggunakan dua J-K flip-flop yang dihubungkan bersama dalam konfigurasi seri. Satu flip-flop bertindak sebagai rangkaian "Master", yang memicu pada tepi utama (leading) pulsa clock sementara yang lain bertindak sebagai rangkaian "Slave", yang memicu pada tepi jatuh (falling) pulsa clock. Ini menghasilkan dua bagian, bagian master dan bagian slave yang diaktifkan selama setengah siklus berlawanan dari sinyal clock.

Toggle Flip Flop

T flip flop merupakan suatu rangkaian flip flop yang dibuat dengan menggunakan flip flop J-K yang mana kedua inputnya dihubungkan menjadi satu (J-K dihubungkan menjadi satu).

Output dari toggle flip-flop (T flip flop), mengubah status setiap kali dipicu pada input T-nya, disebut juga input bolak-balik. Artinya, output menjadi '1' jika '0' dan '0' jika itu '1'.

Gambar masing-masing 10.34 (a) dan (b) menunjukkan simbol rangkaian dari edge-triggered positif dan edge-triggered negatif flip-flop T, bersama dengan tabel fungsinya.

Ketika input J dan K flip-flop terikat ke level aktifnya (logika '1' jika J dan K aktif High, dan '0' level ketika J dan K aktif Low), flip-flop akan berperilaku seperti toggle flip-flop, dengan input clock berfungsi sebagai input T. Gambar 10.36 menunjukkan penggunaan flip-flop J-K sebagai T flip-flop.

4. Percobaan

[Kembali]

a. Prosedur Percobaan

- Buka aplikasi proteus

- Pilih komponen yang akan digunakan, seperti resistor, logic state, logic probe, gerbang NAND, gerbang NOR, gerbang NOT, gerbang AND, dan ground

- Rangkai setiap komponen menjadi rangkaian yang akan dirangkai

- Ubah spesifikasi komponen sesuai kebutuhan

- Jalankan simulasi rangkaian

b. Rangkaian Simulasi

c. Prinsip Kerja Rangkaian

Gambar 10.24 (a) : Jika input U2 berlogika 1 maka outputnya berlogika 0, kemudian input U1 akan berlogika 1 (sama dengan input U2) dan logika 0 (sama dengan output U2), sehingga output U1 berlogika 0. Jika input

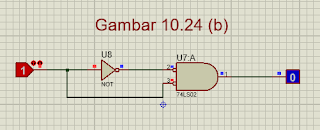

Gambar 10.24 (b) : Jika input U8 berlogika 1 maka outputnya berlogika 0, kemudian input U7:A akan berlogika 1 (sama dengan input U8) dan logika 0 (sama dengan output U8), sehingga output U7:A berlogika 0. Jika input

Gambar 10.25 (a): Ketika input S dan R pada FF U1:A berlogika 1, maka output Q dan -Q akan mengeluarkan output toggle. Ketika input S berlogika 0 dan R berlogika 1 pada FF U1:A, maka output Q akan berlogika 1 dan -Q akan berlogika 0. Ketika input S berlogika 1 dan R berlogika 0 pada FF U1:A, maka output Q akan berlogika 0 dan -Q akan berlogika 1. Namun, jika input S dan R keduanya berlogika 0, maka output Q dan -Q akan berlogika 1.

Gambar 10.25 (b): Ketika input S dan R pada FF U2:A berlogika 1, maka output Q dan -Q akan mengeluarkan output toggle. Ketika input S berlogika 0 dan R berlogika 1 pada FF U2:A, maka output Q akan berlogika 1 dan -Q akan berlogika 0. Ketika input S berlogika 1 dan R berlogika 0 pada FF U2:A, maka output Q akan berlogika 0 dan -Q akan berlogika 1. Namun, jika input S dan R keduanya berlogika 0, maka output Q dan -Q akan berlogika 1.

Gambar 10.26 : Ketika input J dan K berlogika 1, maka output Q dan -Q akan mengeluarkan output toggle. Ketika input J berlogika 0 dan K berlogika 1, maka output Q akan berlogika 0 dan -Q akan berlogika 1. Ketika input J berlogika 1 dan K berlogika 0, maka output Q akan berlogika 1 dan -Q akan berlogika 0. Namun, jika input J dan K keduanya berlogika 0, maka output Q dan -Q dalam kondisi no change.

Gambar 10.27 : Jika input U5 berlogika 1 dan U6 berlogika 0 maka Q akan berlogika 0 dan -Q akan berlogika 1. Sebaliknya, jika input U5 berlogika 0 dan U6 berlogika 1 maka Q akan berlogika 1 dan -Q akan berlogika 0. Namun, jika input U5 berlogika 0 dan U6 berlogika 0 maka Q dan -Q akan mengeluarkan output 1.

Gambar 10.29 (a) : Ketika preset berlogika 1 dan Clear berlogika 0, input U3:A dan U3:B dalam keadaan dont care maka Q akan berlogika 0 dan -Q akan berlogika 1. Ketika preset berlogika 0 dan Clear berlogika 1, input U3:A dan U3:B dalam keadaan dont care maka Q akan berlogika 1 dan -Q akan berlogika 0. Ketika preset berlogika 1 dan Clear berlogika 1, input U3:A dan U3:B berlogika 1 maka Q dan -Q dalam keadaan toggle.

Gambar 10.30 (a) : Ketika kedua input J dan K pada FF U1 berlogika 1, maka output Q dan -Q akan mengeluarkan output toggle. Ketika kedua input J berlogika 1 dan K berlogika 0 pada FF U1, maka output Q akan berlogika 1 dan -Q akan berlogika 0. Ketika kedua input J berlogika 0 dan K berlogika 1 pada FF U1, maka output Q akan berlogika 0 dan -Q akan berlogika 1. Sesuai dengan tabel kebenaran pada gambar 10.30 (b).

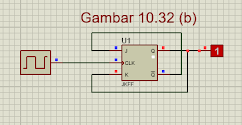

Gambar 10.32 (b): Input Clock dalam keadaan dont care, input J dihubungkan dengan output -Q dan input K dihubungkan dengan output Q, sehingga output FF dalam keadaan toggle.

Gambar 10.32 (c) : Input Clock dalam keadaan dont care, input J dihubungkan dengan output Q dan input K dihubungkan dengan output -Q, sehingga output FF berlogika 0.

Gambar 10.36 : Input J dan K selalu berlogika 1, jika input clock berlogika 0, maka output Q dan -Q dalam keadaan no change. Namun, jika input clock berlogika 1, maka nilai output Q menjadi nilai -Q dan sebaliknya.

d. Video Simulasi

d. Link Download

Download File Proteus

Download Video Simulasi Rangkaian (1)

Download Video Simulasi Rangkaian (2)

Download Datasheet Resistor

Download Datasheet Gerbang AND

Download Datasheet Gerbang NAND

Download Datasheet Gerbang NOT

2. Bentuk gelombang persegi 100 kHz dari gambar 10.32(a) diterapkan pada input clock flip-flop yang ditunjukkan pada gambar 10.32(b) dan (c). Jika output Q awalnya '0', gambar bentuk gelombang output Q dalam dua kasus. Juga, tentukan frekuensi output Q dalam dua kasus.

Gambar (a) menunjukkan gelombang output Q untuk gambar 10.32 (b) dan gambar (b) menunjukkan gelombang output Q untuk gambar 10.32 (c).

5. Example

[Kembali]

1. Gambar simbol sirkuit flip-flop yang diwakili oleh tabel fungsi gambar 10.31(a)!

Solusi:

2. Bentuk gelombang persegi 100 kHz dari gambar 10.32(a) diterapkan pada input clock flip-flop yang ditunjukkan pada gambar 10.32(b) dan (c). Jika output Q awalnya '0', gambar bentuk gelombang output Q dalam dua kasus. Juga, tentukan frekuensi output Q dalam dua kasus.

Solusi:

Gambar (a) menunjukkan gelombang output Q untuk gambar 10.32 (b) dan gambar (b) menunjukkan gelombang output Q untuk gambar 10.32 (c).

Frekuensi bentuk gelombang output Q dalam dua kasus sama dengan setengah frekuensi input clock, untuk alasan yang jelas, dan karena itu 50 kHz.

6. Problem

[Kembali]

1. Jelaskan prinsip kerja rangkaian di bawah!

Jawab:

Jika salah satu atau kedua input U5 dan U6 berlogika 1 maka Q dan -Q akan mengeluarkan output 0 dan 1. Namun, jika kedua input U5 dan U6 berlogika 0 maka Q dan -Q akan mengeluarkan output 1.

2. Jelaskan apa itu toggle flip-flop!

Jawab:

T flip flop merupakan suatu rangkaian flip flop yang dibuat dengan menggunakan flip flop J-K yang mana kedua inputnya dihubungkan menjadi satu (J-K dihubungkan menjadi satu).

7. Soal Pilihan Ganda

[Kembali]

1. Perhatikan rangkaian di bawah!

Jika rangkaian disimulasikan, apa yang akan terjadi pada rangkaain 10.32 (b) dan (c) secara berturut-turut...

a. Output (b) bernilai 1 dan output (c) bernilai 0

b. Output (b) bernilai 0 dan output (c) bernilai 0

c. Output (b) bernilai 0 dan output (c) bernilai 1

d. Output (b) bernilai 1 dan output (c) bernilai 1

2. Perhatikan rangkaian di bawah!

a. Toggle J-K Flip-Flop

b. S-R Flip-Flop

c. Master-Slave J-K Flip-Flop

d. J-K Preset Clear Flip-Flop

Tidak ada komentar:

Posting Komentar