1. Jurnal

[Kembali]

2. Alat dan Bahan

[Kembali]

- Saklar SPDT

- VCC

- Ground

- Gerbang XOR dengan 2 input

- Gerbang OR dengan 2 input

- Gerbang AND dengan 3 input

- Logic Probe

3. Rangkaian Simulasi

[Kembali]

Percobaan 2 terdiri atas 2 rangkaian yang masing-masing rangkaian terdiri atas 1 buah gerbang AND dengan 3 input, 1 buah gerbang OR dengan 2 input, 1 buah gerbang XOR dengan 2 input, 1 buah Logic Probe, 1 buah power, 1 buah ground, dan 4 buah Saklar SPDT.

Jika input A, B, C, dan D pada rangkaian A secara berturut-turut berlogika 0, 1, 1 0, maka input gerbang U2 (input B dan D) berlogika 1 dan 0 sehingga U2 akan memiliki output berlogika 1 (hasil penjumlahan input gerbang XOR yang berlogika 1 nya berjumlah ganjil) dan input gerbang U1 berlogika 0, 0, 0 (Input A, C', dan D) sehingga U1 akan memiliki input 0 (gerbang AND akan memiliki output berlogika 0 jika semua atau salah satu inputnya berlogika 0). Karena U1 memiliki output logika 0 dan U2 memiliki output logika 1 maka input U3 akan berlogika 0 dan 1 sehingga gerbang U3 akan memiliki output logika 1 (output gerbang OR akan berlogika 1 jika semua atau salah satunya inputnya berlogika 1).

Jika input A, B, C, dan D pada rangkaian B secara berturut-turut berlogika 0, 1, 1 0, maka input gerbang U5 berlogika 1 dan 0 (input B dan D) sehingga U5 akan memiliki output berlogika 1 (hasil penjumlahan input gerbang XOR yang berlogika 1 nya berjumlah ganjil) dan input gerbang U4 berlogika 0, 1, 0 (input A, B, dan C') sehingga U4 akan memiliki input 0 (gerbang AND akan memiliki output berlogika 0 jika semua atau salah satu inputnya berlogika 0). Karena U4 memiliki output logika 0 dan U5 memiliki output logika 1 maka input U6 akan berlogika 0 dan 1 sehingga gerbang U6 akan memiliki output logika 1 (output gerbang OR akan berlogika 1 jika semua atau salah satunya inputnya berlogika 1).

Kedua rangkaian dari percobaan 2 ini akan memiliki output rangkaian yang sama. Jika rangkaian A memiliki ouput logika 1 maka rangkaian B juga akan memiliki output logika 1. Sebaliknya, jika rangkaian A memiliki ouput logika 0 maka rangkaian B juga akan memiliki output logika 0.

Gerbang AND

Gerbang AND akan berlogika 1 atau keluarannya akan berlogika 1 jika semua inputannya berlogika 1. Namun, jika semua atau salah satu inputnya berlogika 0 maka outputnya akan berlogika 0.

Gerbang OR

Gerbang OR akan berlogika 1 jika salah satu atau semua inputnya berlogika 1 dan akan berlogika 0 jika semua inputnya berlogika 0.

Gerbang XOR

Gerbang XOR merupakan kepanjangan dari Exclusive OR yang mana outputnya akan berlogika 1 apabila semua inputannya berbeda, namun apabila inputannya sama maka akan memberikan output berlogika 0. Gerbang XOR dengan input lebih dari 2 akan berlogika 1 jika hasil penjumlahan input logika 1 berjumlah ganji dan akan berlogika 0 jika hasil penjumlahan input logika 1 berjumlah genap.

5. Video Simulasi

[Kembali]

6. Analisa

[Kembali]

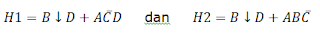

Jelaskan bagaimana mendapatkan H1 dan H2 menggunakan Aljabar Boolean dan Peta Karnaugh!

Jawab:

7. Link Download

[Kembali]

Tidak ada komentar:

Posting Komentar